チュートリアル

GPIO 4bit / 2bit / SPI接続

この項目では、GPIO4bit/2bit,SPI接続等の汎用ポートを使用した接続方法の手順を解説しております。

本手順では、通常のテストポイント情報を取得するまでに変更が必要な個所について御説明いたします。

実際導入を行う際には、お客様の環境に合わせてDT10の導入を行ってください。

1.出力ポートのレジスタ設定の調査

汎用ポート接続では、DynamicTracerと接続するポートのHI/LOW制御が必要になります。

出力ポートのレジスターのアドレスを調査頂き、使用するポートを出力ポートに設定してください。

2.サンプルドライバの構成

Driver_DT10

-dt10_tpdrv.c … ユーザーランド側の出力用ドライバ。

カーネル層のデバイスドライバをコールしWriteする。

Driver_xxx

-dt_xxx_drv.c … カーネル側の出力用のデバイスドライバ

(※”xxx”の部分は各接続方式になります。)

ご入手いただいたサンプルドライバは、以下のフォーマットでデータを出力するようになっております。

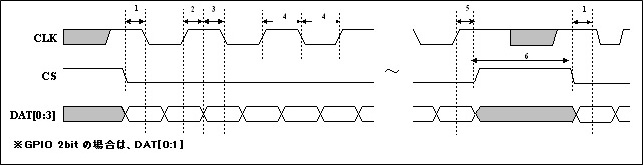

■GPIO 4bit/2bit 接続出力フォーマット

・データは、4bit/2bit パラレル転送とし、以下の項目順序でMSB First 出力となります。

・ラッチタイミングは、CLK の立ち上がりと立ち下りの両エッジです。

※4bit の場合は、addr のビット数は可変長(0/4/8/12/16/20/24)とし、24bit に満たない分の上位ビットはゼロと

して扱われます。

※2bit の場合は、addr のビット数は可変長(0/2/4/6/8/10/12/14/16/18/20/22/24)とし、24bit に満たない分

の上位ビットはゼロとして扱われます。

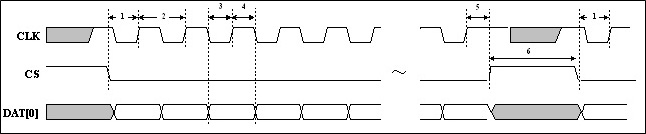

■SPI 接続出力フォーマット

・データは、1bit シリアル転送とし、以下の項目順序でMSB First 出力とします。

・ラッチのタイミングは、CLK の立ち上りエッジです。

① _TP_BusOut()の引数 dat (16bit)

② _TP_BusOut()の引数 addr (0~24bit)

※addr のビット数は可変長とし、24bit に満たない分の上位ビットはゼロとして扱われます。

3. カーネル用デバイスドライバのカスタマイズ

ダウンロードいただいたファイルについて、下記の内容をターゲット環境に合わせてご変更ください。

3-1. 出力ポート定義の設定

/*==============================================================================*/

/* Desc: GPIO Control setting */

/*==============================================================================*/

#define CS_BIT 7 /* CS */

#define CLK_BIT 25 /* CLK */

#define DATA0_BIT 8 /* DATA0 */

#define DATA1_BIT 9 /* DATA1 */

#define DATA2_BIT 10 /* DATA2 */

#define DATA3_BIT 11 /* DATA3 */

GPIO4bit/2bit,SPI接続で使用する出力ポートの設定を行ってください。

上記の例はGPIO4bitの例となっております。

GPIO4bit/2bitの場合は、使用する4、または2ポートを定義してください。

3-2. 出力制御マクロの修正

サンプルドライバでは、各ポートのHI/LOW制御をマクロで操作しております。

以下のマクロを御社環境に合わせてご変更ください。

#define INP_GPIO(g) iowrite32(\

ioread32( (void*)((int *)iop+(g)/10) ) & ~(7<<(((g)%10)*3)), \

(void*)((int *)iop+(g)/10) )

#define OUT_GPIO(g) iowrite32(\

ioread32( (void*)((int *)iop+(g)/10) ) | (1<<(((g)%10)*3)), \

(void*)((int *)iop+(g)/10) )

#define GPIO_SET(g) iowrite32( 1<<(g), (void*)((int *)iop+7) )

#define GPIO_CLR(g) iowrite32( 1<<(g), (void*)((int *)iop+10) )

#define GPIO_GET ioread32((void*)((int *)iop+13))

使用する各ポートを制御するマクロ定義です。iowrite/readを使用しポートレジスタを制御しています。

もし上記のような定義が難しい場合であれば、ターゲット環境が用意しているポート制御用のKernelAPIを使用する形でも構いません。

“#include

”

#define CLK_CS_HI { \

GPIO_SET(CS_BIT); \

GPIO_SET(CLK_BIT); \

}CS,CLKポートを両方HIにするマクロです。

ポート制御レジスターをターゲットに合わせてご変更ください。

#define CS_HI { \

GPIO_SET(CS_BIT); \

}

#define CS_LOW { \

GPIO_CLR(CS_BIT); \

}

#define CLK_HI { \

GPIO_SET(CLK_BIT); \

}

#define CLK_LOW { \

GPIO_CLR(CLK_BIT); \

}

CLK、CSの各ポートのHI/LOWにするマクロです。上記のCLK_CS_HI同様、ご変更ください。

なお、CLKについてはGPIOの場合のみの設定となります。

■GPIO 4bit/2bit の場合

#define DATA_OUT(x) { \

( (x) & 0x1) ? GPIO_SET(DAT0_BIT) : GPIO_CLR(DAT0_BIT); \

( (x) & 0x2) ? GPIO_SET(DAT1_BIT) : GPIO_CLR(DAT1_BIT); \

( (x) & 0x4) ? GPIO_SET(DAT2_BIT) : GPIO_CLR(DAT2_BIT); \

( (x) & 0x8) ? GPIO_SET(DAT3_BIT) : GPIO_CLR(DAT3_BIT); \

}

■SPI の場合

#define DATA_OUT(x) { \

GPIO_CLR(CLK_BIT); \

if( (x) ){ \

GPIO_SET(DAT0_BIT); \

} \

else{ \

GPIO_CLR(DAT0_BIT); \

} \

GPIO_SET(CLK_BIT); \

}

DATA、CLKそれぞれのポートのHI/LOWにするマクロです。GPIOと違い、CLK側の制御もこちらで行っております。

xには0かそれ以外ののデータが渡されます。

DAT0-3ないし0-1の各ポートのHI/LOWにするマクロです。

xには4bitないし2bitのデータが渡されます。

3-3. 各種Include,defineの設定

/*==============================================================================*/

/* Desc: Header for PORT Control */

/*==============================================================================*/

#include

#include

#include // printk ();

#include // everything

#include // error codes

#include // size_t

#include // O_ACCMODE

#include // cli(); *_flags

#include // copy_from/to_user

#include // cdev struct.

#include // gettid();

#include

#include

#define LICENSE "GPL v2"

各ポートのコントロール等に必要なヘッダファイルをIncludeしてください。

4.ユーザーランド用ドライバのカスタマイズ

ユーザーランド層のドライバについては基本的にカスタマイズは必要ございません。

テストターゲットアプリと同様の環境に入れていただき、Make対象としてください。

5.カーネル、ユーザランドのコンパイル

お使いの開発環境にご変更いただいたドライバファイルを追加します。

Makefileに追加していただくなどして、コンパイルできるかご確認ください。