新製品「DT+シリーズ」がリリースされ早2カ月。

性能評価で活躍したFPGAファームウェア開発シリーズの第2弾です。

今回の「はじめてのFPGAファームウェア開発」では、

前回の記事でちょっとだけ出てきたハードウェア記述言語で使用される考え方「並列処理」に着目。

C言語などのソフトウェア言語との違いについて触れていきたいと思います。

CONTENTS

ハードウェア記述言語とは?

まずは前回のおさらい、「ハードウェア記述言語」とは何ぞや?を説明します。

ハードウェア記述言語”HDL(Hardware Description Language)”とは、FPGA(Field Programmable Gate Array)などを制御するための言語です。

デバイスの演算素子の配線を自由にカスタマイズできます。

特徴としては、基本的に複数の命令が全て同時に処理(並列処理)されるという点が挙げられます。

“VHDL”や”Verilog HDL”といった2種類の言語が多く使われているようです。

詳細は、過去記事「はじめてのFPGAファームウェア開発 ~ 開発未経験者がデバッグ治具を作ってみた ~」でも記載していますので、こちらもチェックしてみてください。

ソフトウェア言語とは?

続いて、「ソフトウェア言語」とは何ぞや?を説明します。

こちらは、ソフトウェアエンジニアの人であれば、一度は必ず、というか普段から触れているものだと思います。

ハードウェア記述言語と違い、逐次処理が基本で、プログラミングした命令が、上から順番に実行されていきます。

“プログラミング言語”とも呼ばれ、C言語、C++、C#、Java、HTML、Javascript、Pythonなど、様々な種類があります。

並列処理と逐次処理の違い

さて、ここまでハードウェア記述言語・ソフトウェア言語のそれぞれを簡単に見てみました。

ハードウェア記述言語は並列処理、ソフトウェア言語は逐次処理とありましたが、具体的にはどういうことを指すのでしょうか。

今回は、以下のような条件で簡単に例を示してみました。

・並列・逐次処理共に、1つのループ処理の中に以下3つの処理を順番通り記述する

1. ループするたびに、Add1 は前回値+1、Add2 は前回値+2される

2. Sum にAdd1とAdd2 を足した結果を代入する

3. Diff にSum からAdd2 の値を引いた結果を代入する

それぞれの考え方がどうなるか見ていきましょう。

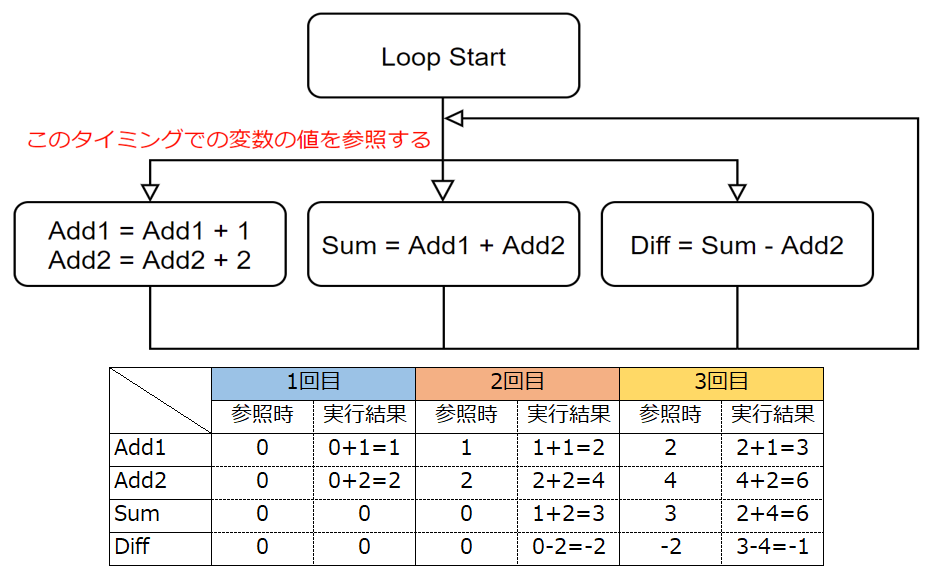

並列処理

並列処理では、記述した順番に関わらず、図1のように命令が全て同時に実行されます。

変数の参照のタイミングも同時です。

同時に実行されるということは、処理の記述が前後しても結果は同じになります。

この結果にある通り、今回のSum やDiff といった、加減算の結果は1ループ前で処理された結果の値を使用して演算されることになります。

逐次処理

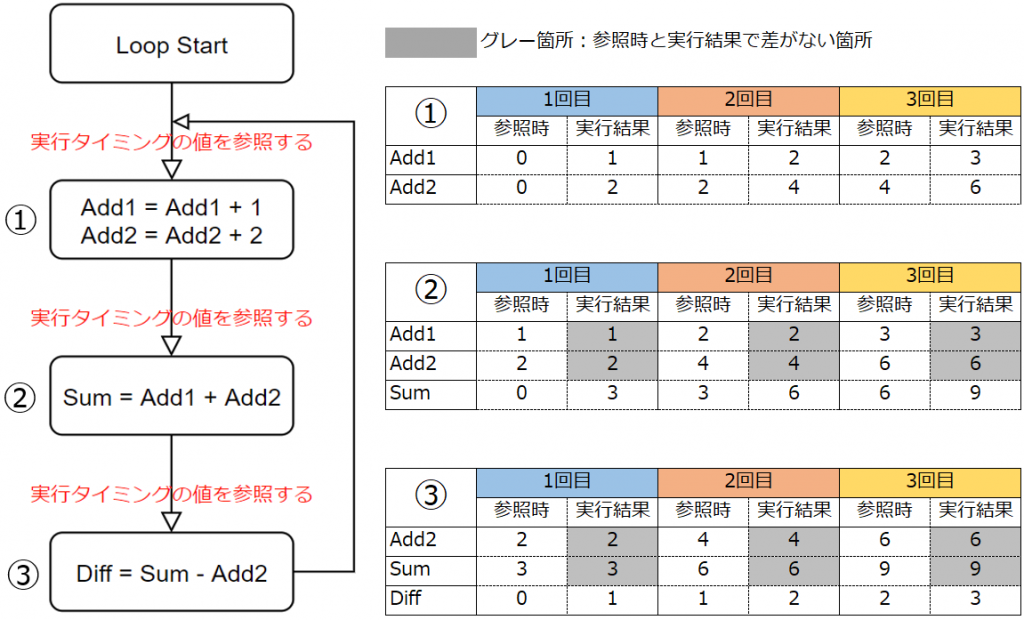

一方、逐次処理(順次処理と呼ばれるときもある)では、記述した順番通りに実行されます。

図2左側のフローのように、上から順番に命令が実行されていき、変数の参照タイミングは使用するたびに該当の変数を参照します。

処理の順番が入れ替わってしまえば、当然実行結果も異なってきます。

この結果を見てみると、同じループの中でも最新の実行結果が参照するたびに反映されていることがわかります。

このように並列処理は、記述が全て同時に実行され、逐次処理は順番通りに実行されます。

ハードウェア記述言語では、前者の並列処理で基本的には構成されますが、逐次処理をする箇所もあります。

VHDLの例を挙げると、process文が逐次処理を行います。つまり、VHDLで逐次処理をさせるには、process文の中に記述する必要があります。

さらに、process文の中に記述できる構文として、case文やif文がありますが、それぞれが並列処理・逐次処理の考え方を必要とするなど複雑になっています。

いずれにせよ、並列処理という使い方を理解しておくことで、きちんとした設計というものが実現できるのではないでしょうか。

if文やcase文といった構文の細かい解説はまた別の機会に紹介できればと思います。

まとめ

今回は軽めな内容でしたが、特にはじめてハードウェア記述言語に触れた人が、考え方でつまづいてしまいそうなところをピックアップしてみました。

ハードウェアならではの、記述されている命令文が同時に実行されるという感覚を掴むまでが意外と難しく、挫折してしまう人も多いようです。

ifやcaseなど論理方向が分かれるタイミングの処理で、変数を参照するタイミングを勘違いしたまま実装してしまうと、設計からやり直す必要が出てきてしまうなど、手戻りも増えてしまいます。

C言語の経験があるから…if文などのなじみのある命令文もあるしすぐわかりそう!などと高をくくっていたら大変。

私自身もふわっと理解している状態で実装してみましたが、思ったような動作をせずに、でもどこがおかしいのかがわからず…

ソフトウェア言語でのプログラム経験があったがゆえに、理解するのにとても苦労をしました。

先輩の「FPGAでのファーム開発は、処理のフローを考えることが非常に重要だ」という言葉にならうと、正しい設計をするためには「並列処理」という考え方をきちんと理解しておく必要があると思いました。

並列処理を制する者はハードウェア記述言語を制する!

というのは言い過ぎかもしれませんが、きちんとマスターしておきたいですね。

前回記事「開発未経験者がデバッグ治具を作ってみた」はコチラ!