まもなく弊社の動的テストツールの新製品「DT+シリーズ」がご提供可能となります。

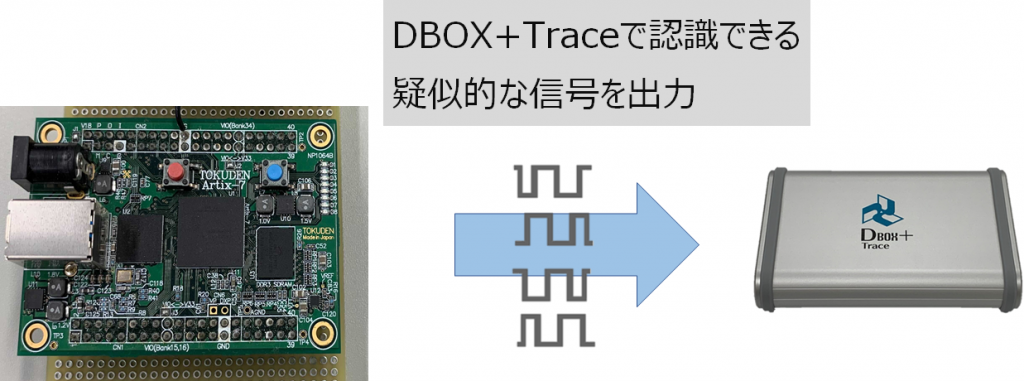

私は、そのDT+シリーズの新しいハードウェアである「DBOX+Trace」の開発に携わっているのですが・・・。

新製品開発における私のミッションは、

「DBOX+Traceの性能評価として、信号検知の限界速度やデータ取得能力を計測すること」

でした。

そして、その性能評価のためには、

以下のように、DBOX+Traceに様々な仕様の疑似的なトレース信号を入力しなければなりません。

そこで、FPGAの開発を習得し、

FPGAの高速処理や自在に回路変更できるメリットを利用したデバッグ治具を作る必要がありました。

しかし、私は今までFPGAやハードウェア記述言語といったものに触れたことはなかったのです・・・。

FPGAって初学者には結構ハードル高め

まずは下調べということで、インターネットで開発方法や言語について調べてみましたが、

専門用語が飛び交う中で、初学者向けの文献がなかなか見つかりませんでした。

専門書もいくつか読みましたが、開発経験のある先輩がいなかったら、FPGA開発の習得はかなり難しかったものと思います。

そういった背景もあり、私と同じような初学者の方にとって価値のある記事を残しておきたいと思い、このブログを執筆した次第です。

FPGAとは?

FPGAとは、「Field Programmable Gate Array」の略で、現場で動作を改変出来るゲートアレイと直訳できます。

つまり、プログラム次第でいかようにでもなるデバイスということです。

プログラムによって演算素子の配線を自由自在に変更可能です。

マイコンはCPUやメモリが搭載されており、C言語などの言語で書かれたプログラムを実行することで、

CPUがプログラムに書かれている通りに処理をします。

一方、FPGAはマイコン内部のCPU自体のイメージです。

FPGAはその名の通り、HDLなどでプログラムすることで自由に動作を変えられます。

プログラム通りに動いてくれるLSIを作るようなイメージです。

また、FPGAは非常に高速な処理が可能です。

通常のマイコンの処理速度では実現できない処理でも、FPGAを使えば実現できちゃう、そんなデバイスです。

例えば、テレビやオーディオ機器などをはじめ、通信インフラに関わる装置など、高速でデジタル信号の処理が必要なものに搭載されています。

最近では、IoT機器やAIの開発なんかにも使われていると耳にしたことがあります。

FPGA開発への準備

今回は一例として、私が開発で使ったものをピックアップしてみました。

まずはやってみることが大切で、実際に動かせる評価ボードを購入して、いろいろと触ってみるのが習得への近道です。

- 開発用PC

-OS:Windows10 64bit CPU:AMD Ryzen7 4700U メモリ:16GB - FPGA開発環境

-Xilinx社 Vivado HLx v2018.2 WebPACK(無償版) - FPGA評価基板

-特殊電子回路株式会社 TKDN_ART7_BRD - FPGAのピン定義ファイル

-自作することも可能だが、今回使用した評価基板は、製品ページに定義ファイルがあったので、そちらを採用 - FPGA書き込みツール

-オンボードUSB-JTAGツール”s6a7jtagw.exe” こちらも製品ページにツールがあったので採用 - オシロスコープ

-出力されている波形を計測するために使用。

単純Hi/Loを見るだけであれば、ハンドテスターで代用も可

開発環境のインストール

用意した評価ボードに搭載されているチップに合わせた開発環境をインストールします。

ここからは、今回私が使用したツールの段取りに基づいて記載していきます。

実際は使用する開発環境やバージョンによって異なります。

今回私が使用したXilinx社のVivadoは、公式HPからダウンロードできました。

基本的には初期設定で問題ありませんが、Xilinxのアカウントを作る必要がありました。

エディションはWebPACKを使用しています。(ほかのエディションは有料のようです)

プロジェクトの作成

プロジェクトの名前や、プロジェクトのタイプを指定します。

私の使用した環境では、RTLプロジェクトとして作成できました。

そのほか、I/Oの結線のみの設定や、他のプロジェクトからインポートする設定などがあるようです。

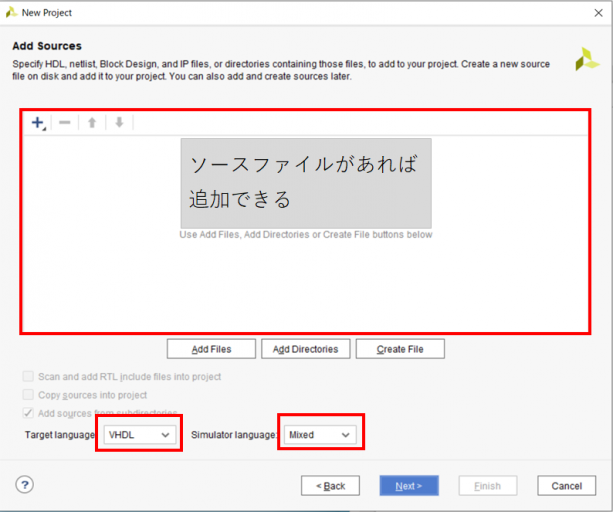

次に、ソースファイルの追加画面です。

ソースファイルの元となるファイルなどがあれば登録できますが、後からでも当然登録できるので、

わからなければそのままで問題ありません。

Target languageはVHDLを指定し、Simulator languageはMixedを指定しました。

次に、制約ファイルの追加画面です。

ピン定義ファイルなどがあれば登録できます。

拡張子は.xdcや、.ucfといったファイルです。

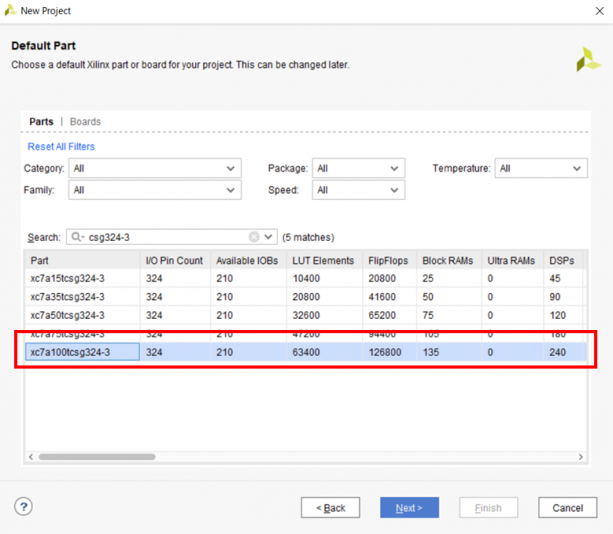

最後に、ボードの指定です。

今回は、xc7a100tcsg324-3を使用します。

対応ボードが非常に多いのですが、検索機能ですぐに見つけ出せます。

以上で、プロジェクトの作成は完了です。

プログラムの書き方

冒頭でも説明した通り、FPGAのプログラムはハードウェア記述言語”HDL”(Hardware Description Language)で書かれます。

ハードウェア記述言語にはいくつか種類があります。

今回は”VHDL“(VHSIC Hardware Description Language)を使用しました。※VHSIC(Very High Speed Integrated Circuitsの略)

VHDLの他に、Verilog HDLなどがよく使われます。

名前が似ていますが記述方法が違うので注意が必要です。

では、実際にVHDLの中身についてみていきましょう。

(コーディングまでの設定は使用する環境によって異なりますので、今回は割愛します)

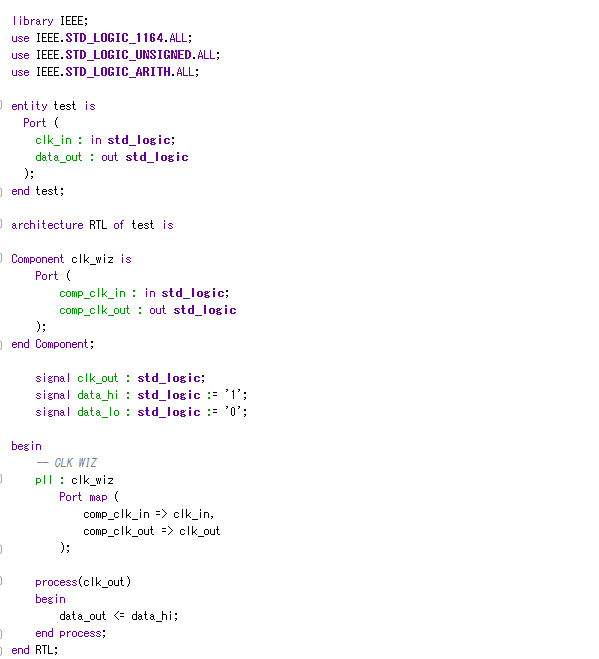

VHDLは大きく分けると、以下のようなブロックで分けられます。

- ライブラリ定義部

-パッケージ指定 - entity部

-ポート宣言 - architecture部

-component宣言

-論理回路の記述

これらについて説明していきます。

ライブラリ定義部

ここには、使用するパッケージの呼び出しなどを記載していきます。

-- パッケージ指定 library IEEE; -- IEEEライブラリを使用 use IEEE.STD_LOGIC_1164.ALL; -- 基本的な関数 use IEEE.STD_LOGIC_UNSIGNED.ALL; -- 符号なし演算に必要 use IEEE.STD_LOGIC_ARITH.ALL; -- 符号のありなしに関わらず演算に必要 -- (ハイフン2つ)で以降の記述がコメント扱いになる

上記に記載したものは、最初のうちはおまじない的に書いておくと良いでしょう。

具体的な内容は各記述の後半にコメントとして記載をしておきました。

entity部

ここには、ポートの宣言などを記載していきます。

entity "エンティティ名" is

Port (

-- ピン定義ファイルで定義されているピン名 : 入出力の指定

-- 以下は例とします

clk_in : in std_logic;

data_out : out std_logic

);

end "エンティティ名";

architecture部

ここには、使うモジュールの宣言や変数宣言、実際の回路の動作などを記載していきます。

アーキテクチャ名にはよく”RTL”(Register Transfer Level)という名称をつけます。

“begin”の前をarchitecture宣言部、後をarchitecture本体などと呼びます。

architecture宣言部には、モジュールの宣言(component)や、変数宣言(signal)などを記述し、

architecture本体には、実際の回路動作などを記述します。

architecture "アーキテクチャ名" of "エンティティ名" is

-- コンポーネント文

-- 別ファイルの処理を、モジュールとして呼び出したりする場合に記述する

-- このファイルから見て、下位の階層として扱われる

Component "コンポーネント名" is

Port (

-- 以下は例とします

comp_clk_in : in std_logic;

comp_clk_out : out std_logic

);

end Component;

-- signal "変数名" : 型の指定;

-- signal "変数名" : 型の指定 := "'初期値'"; で初期値を入れることも可能

-- 以下は例とします

signal clk_out : std_logic;

signal data_hi : std_logic := '1';

signal data_lo : std_logic := '0';

begin

-- "インスタンス名" : "下位の階層のエンティティ名"

-- インスタンス名は、コンポーネント文で記述した下位の階層のモジュール名を

-- このファイルから見たときの固有の名前として識別する

-- port map ( "下位の階層のポート" => "このファイルでの信号" );

-- port mapでは、下位の階層のポートをこのファイルの信号と接続する

-- 以下は例とします

pll : clk_wiz

Port map (

comp_clk_in => clk_in,

comp_clk_out => clk_out

);

-- process文

-- 回路記述をする

-- process ("入力信号") begin "実行処理" end process;

-- 入力信号は"センシティビティ・リスト"と呼ばれ、その信号に変化があると実行処理が実行される

-- end processまでたどり着くと、センシティビティ・リストの信号が変化するまで動作しない

-- 以下は例とします

process(clk_out)

begin

data_out <= data_hi;

end process;

end "アーキテクチャ名";

では、各詳細のコメントを抜いたコードを見てみましょう。

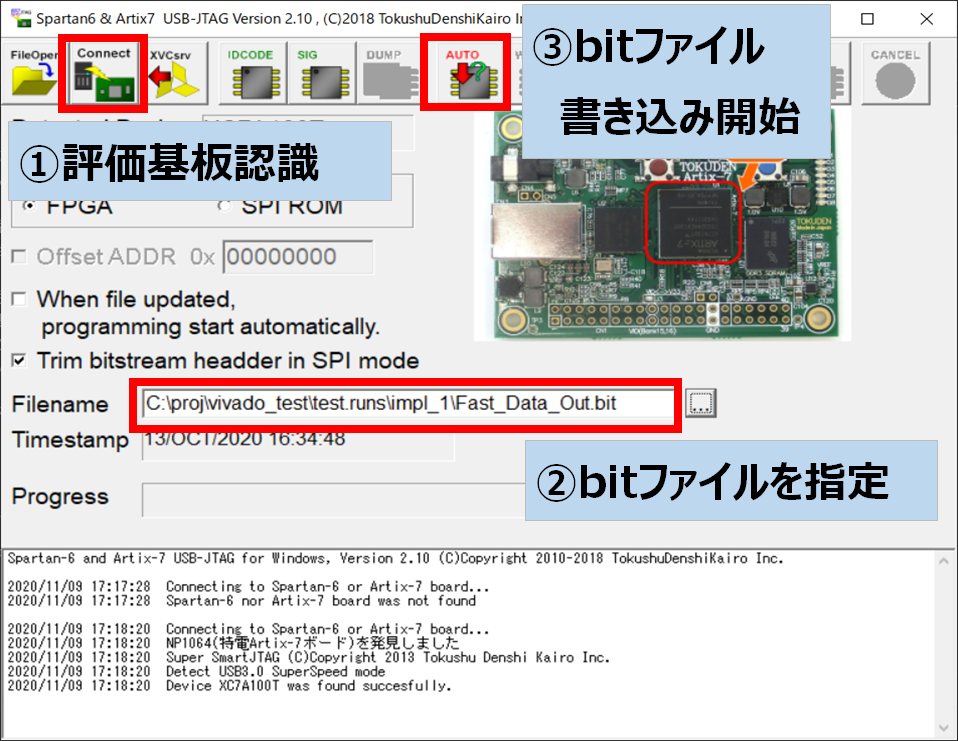

記述が完了したら、bitファイルを生成し、JTAG経由で書き込みをします。

通常、よくある開発環境では、”bitstream”などといったキーワードの辺りでbitファイルが生成できます。

今回は、特殊電子回路株式会社指定のアプリ”s6a7jtagw.exe”を使い、評価基板に書き込みを行いました。

今回使ったVivadoでは、”[プロジェクトフォルダ]\[プロジェクト名].runs\impl_1″の中にbitファイルが生成されていました。

(bitファイルが見つからずに一苦労しました)

bitファイルを書きこみ、指定されているピンをオシロスコープで見てあげると、信号がHiになっているはずです。

今回私が使用したVivadoでは、Clocking Wizardというものがあり、クロックの設定がGUIで簡単にできました。

Clocking Wizardでクロック信号の数や周波数を設定するだけでモジュール化してくれるので、

そのモジュールをコンポーネントとして宣言することで、クロック生成に手間をかけずに実装できました。

FPGAを使ってみた感想

先輩曰く、「FPGAでのファーム開発は、処理のフローを考えることが非常に重要だ」とのことです。

私も実際にデバッグをしてみて実感しましたが、C言語的な考え方とはまた違って、

全ての処理が同時に実行されていくというハードウェア特有の動作の感覚がなかなか掴めずに苦労しました。

今回は、FPGAを使って単純にLo/Hi信号を出力する内容までとなります。

この信号をある周期でHi/Loさせたり、決められた固定値を順に出力したりと、コーディングによって自由自在に動作を変更できます。

今後もFPGAの開発実績をブログで公開していきたいと思います。

これからFPGAに触れる方は是非チェックしてください。

次の記事「並列処理を理解する」はコチラ!

【無料セミナー動画】動的テストの事例紹介!

組込み機器開発特有のソフトウェアデバッグ、テストにお困りではありませんか?

初期化処理や処理時間、複数CPUのシーケンス処理など、どのようにテストしていますか?

複数の機器で構成されたシステムでは、

「機器同士のやりとりを把握することができない」

「デバッガを使ってブレークをかけることができない」

といった問題にぶつかり、ソフトウェア内部の動きを把握することは困難です。

そこで今回は、動的テストツールDT+ユーザー様を講師にお迎えし、

このような課題に対する活用事例をご紹介させていただきます。